## Fundamentals of

# DIGITAL LOGIC with VHDL DESIGN

## FUNDAMENTALS OF DIGITAL LOGIC WITH VHDL DESIGN

## **FOURTH EDITION**

## Stephen Brown and Zvonko Vranesic

Department of Electrical and Computer Engineering University of Toronto

### FUNDAMENTALS OF DIGITAL LOGIC WITH VHDL DESIGN, FOURTH EDITION

Published by McGraw Hill LLC, 1325 Avenue of the Americas, New York, NY 10019. Copyright © 2023 by McGraw Hill LLC. All rights reserved. Printed in the United States of America. Previous editions © 2009, 2005, and 2000. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written consent of McGraw Hill LLC, including, but not limited to, in any network or other electronic storage or transmission, or broadcast for distance learning.

Some ancillaries, including electronic and print components, may not be available to customers outside the United States.

This book is printed on acid-free paper.

1 2 3 4 5 6 7 8 9 LCR 27 26 25 24 23 22

ISBN 978-0-07-338072-8 (bound edition) MHID 0-07-338072-5 (bound edition) ISBN 978-1-259-82897-3 (loose-leaf edition) MHID 1-259-82897-2 (loose-leaf edition)

Portfolio Manager: *Beth Bettcher* Product Developer: *Erin Kamm* Marketing Manager: *Lisa Granger*

Content Project Managers: Maria McGreal, Samantha Donisi

Buyer: Susan K. Culbertson

Content Licensing Specialist: Shawntel Schmitt Cover Image: View Stock/Getty Images

Compositor: Aptara<sup>®</sup>, Inc.

All credits appearing on page or at the end of the book are considered to be an extension of the copyright page.

### Library of Congress Cataloging-in-Publication Data

Names: Brown, Stephen D., author. | Vranesic, Zvonko G., author.

Title: Fundamentals of digital logic with VHDL design / Stephen Brown and Zvonko Vranesic, Department of Electrical and Computer Engineering,

University of Toronto.

Description: Fourth edition. | New York, NY : McGraw Hill, [2023] | Includes

ndex

Identifiers: LCCN 2021039775 (print) | LCCN 2021039776 (ebook) | ISBN 9780073380728 (hardcover; acid-free paper) | ISBN 9781259828973 (spiral

bound; acid-free paper) | ISBN 9781266711381 (ebook) | ISBN

9780077496111 (ebook other)

Subjects: LCSH: Logic circuits—Design and construction—Data processing. | Logic design—Data processing. | VHDL (Computer hardware description language)

Classification: LCC TK7888.4 .B76 2023 (print) | LCC TK7888.4 (ebook) |

DDC 621.39/5-dc23

LC record available at https://lccn.loc.gov/2021039775

LC ebook record available at https://lccn.loc.gov/2021039776

The Internet addresses listed in the text were accurate at the time of publication. The inclusion of a website does not indicate an endorsement by the authors or McGraw Hill LLC, and McGraw Hill LLC does not guarantee the accuracy of the information presented at these sites.

## **ABOUT THE AUTHORS**

**Stephen Brown** received the Ph.D. and M.A.Sc. degrees in Electrical Engineering from the University of Toronto, and his B.A.Sc. degree in Electrical Engineering from the University of New Brunswick. He joined the University of Toronto faculty in 1992, where he is now a Professor in the Department of Electrical & Computer Engineering. He is also the Director of FPGA Academic Programs for Intel Corporation.

His research interests include field-programmable VLSI technology, CAD algorithms, computer architecture, and applications of machine learning. He won the Canadian Natural Sciences and Engineering Research Council's 1992 Doctoral Prize for the best Ph.D. thesis in Canada, and the New Brunswick Governor-General's 1985 award for the highest academic standing in the Faculty of Engineering. He is a coauthor of more than 150 scientific research papers and two other textbooks: *Fundamentals of Digital Logic with Verilog Design* and *Field-Programmable Gate Arrays*.

He has won many awards for excellence in teaching electrical engineering, computer engineering, and computer science courses.

**Zvonko Vranesic** received his B.A.Sc., M.A.Sc., and Ph.D. degrees, all in Electrical Engineering, from the University of Toronto. From 1963 to 1965 he worked as a design engineer with the Northern Electric Co. Ltd. in Bramalea, Ontario. In 1968 he joined the University of Toronto, where he is now a Professor Emeritus in the Department of Electrical & Computer Engineering. During the 1978–79 academic year, he was a Senior Visitor at the University of Cambridge, England, and during 1984–85 he was at the University of Paris, 6. From 1995 to 2000 he served as Chair of the Division of Engineering Science at the University of Toronto.

He is a coauthor of four other books: *Computer Organization and Embedded Systems*, 6th ed.; *Fundamentals of Digital Logic with Verilog Design*, 3rd ed.; *Microcomputer Structures*; and *Field-Programmable Gate Arrays*. In 1990, he received the Wighton Fellowship for "innovative and distinctive contributions to undergraduate laboratory instruction." In 2004, he received the Faculty Teaching Award from the Faculty of Applied Science and Engineering at the University of Toronto.

He has represented Canada in numerous chess competitions. He holds the title of International Master.

## **PREFACE**

This book is intended for an introductory course in digital logic design, which is a basic course in most electrical and computer engineering programs. A successful designer of digital logic circuits needs a good understanding of the classical methods of logic design and a firm grasp of the modern design approach that relies on computer-aided design (CAD) tools.

The main goals of this book are (1) to teach students the fundamental concepts of classical manual digital design and (2) illustrate clearly the way in which digital circuits are designed today, using CAD tools. Even though current modern designers very rarely use manual techniques, our motivation for teaching such techniques is to give students an intuitive feeling for how digital circuits operate. The manual techniques also provide an illustration of the types of manipulations performed by CAD tools, giving students an appreciation of the benefits provided by design automation. Throughout the book, basic concepts are introduced by way of simple design examples, which we perform using both manual techniques and modern CAD-tool-based methods. After basic concepts are established, more complex examples are provided using the CAD tools. Thus, to illustrate how digital design is presently carried out in practice, our emphasis is on modern design methodology.

## **TECHNOLOGY**

This book discusses modern digital circuit implementation technologies. The emphasis is placed on programmable logic devices (PLDs), which is the most appropriate technology for use in a textbook for two reasons. First, PLDs are widely used in practice and are suitable for almost all types of digital circuit designs. In fact, students are more likely to be involved in PLD-based designs at some point in their careers than in any other technology. Second, circuits are implemented in PLDs by end-user programming. Therefore, students can be provided with the opportunity, in a laboratory setting, to implement this book's design examples in actual chips. Students can also simulate the behavior of their designed circuits on their own computers. We use the two most popular types of PLDs for targeting of designs: complex programmable logic devices (CPLDs) and field-programmable gate arrays (FPGAs).

We emphasize the use of a hardware description language (HDL) in specifying the logic circuits, because an HDL-based approach is the most efficient design method to use in practice. We describe in detail the IEEE Standard VHDL language and use it extensively in examples.

## SCOPE OF THE BOOK

This edition of the book has been extensively restructured. All of the material that should be covered in a one-semester course is now included in Chapters 1 to 6. More advanced material is presented in Chapters 7 to 11.

PREFACE

vii

Chapter 1 provides a general introduction to the process of designing digital systems. It discusses the key steps in the design process and explains how CAD tools can be used to automate many of the required tasks. It also introduces the representation of digital information.

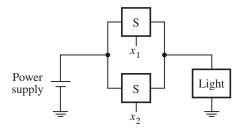

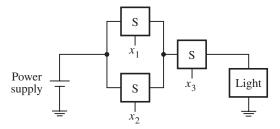

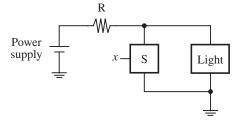

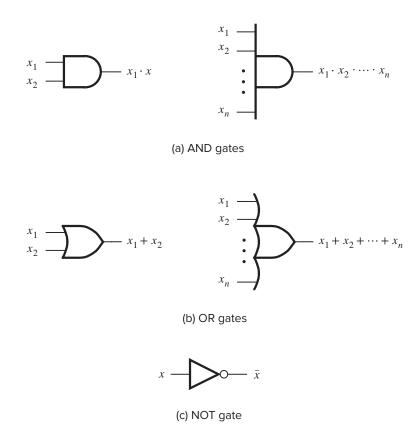

Chapter 2 introduces logic circuits. It shows how Boolean algebra is used to represent such circuits. It introduces the concepts of logic circuit synthesis and optimization, and shows how logic gates are used to implement simple circuits. It also gives the reader a first glimpse at VHDL, as an example of a hardware description language that may be used to specify the logic circuits.

Chapter 3 concentrates on circuits that perform arithmetic operations. It discusses numbers and shows how they can be manipulated using logic circuits. This chapter illustrates how VHDL can be used to specify a desired functionality and how CAD tools can provide a mechanism for developing the required circuits.

Chapter 4 presents combinational circuits such as multiplexers, encoders, and decoders that are used as building blocks in larger circuits. These circuits are very convenient for illustrating the application of many VHDL constructs, giving the reader the opportunity to discover more advanced features of VHDL.

Chapter 5 introduces storage elements. The use of flip-flops to realize regular structures, such as shift registers and counters, is discussed. VHDL-specified designs of these structures are included.

Chapter 6 gives a detailed presentation of synchronous sequential circuits (finite state machines). It explains the behavior of these circuits and develops practical techniques for both manual and automated design.

Chapter 7 is a discussion of a number of issues that arise in the design of digital logic systems. It reveals and highlights problems that are often encountered in practice, and explains how they can be overcome. Examples of larger circuits illustrate a hierarchical approach in designing digital systems. Complete VHDL code for these circuits is presented.

Chapter 8 deals with more advanced methods for optimized implementation of logic functions. It presents algorithmic techniques for optimization, and also explains how logic functions can be specified using a cubical representation or binary decision diagrams.

Chapter 9 discusses asynchronous sequential circuits. While this treatment is not exhaustive, a clear indication of the main characteristics of such circuits is provided. Even though asynchronous circuits are not used extensively in practice, they provide an excellent vehicle for gaining a more complete understanding of the operation of digital circuits. Asynchronous circuits illustrate the importance of clearly understanding how the structure of a circuit affects the propagation delays of signals, and how these delays can impact a circuit's functionality.

Chapter 10 presents a complete CAD flow that a designer experiences when creating, implementing, and testing a digital circuit.

Chapter 11 introduces the topic of testing. A designer of logic circuits must be aware of the need to test circuits and should be conversant with at least the most basic aspects of testing.

Appendix A provides a complete summary of VHDL features. Although use of VHDL is integrated throughout the book, this appendix provides a convenient reference that the reader may occasionally consult while writing VHDL code.

Appendix B presents the electronic aspects of digital circuits. This appendix shows how the basic gates are built using transistors and presents various factors that affect circuit performance. The most modern technologies are emphasized, with particular focus on CMOS technology and PLDs.

## WHAT CAN BE COVERED IN A COURSE

Much of the material in the book can be covered in 2 one-quarter courses. Thorough coverage of the most important material can be achieved in a single one-semester, or even a one-quarter, course. This is possible only if the instructor does not spend too much time discussing the intricacies of VHDL and CAD tools. To make this approach possible, we organized the VHDL material in a modular style that is conducive to self-study. Our experience in teaching students at the University of Toronto has shown that the instructor may only spend a total of three to four lecture hours on VHDL, describing how the code should be structured (including the use of design hierarchy) using scalar and vector variables, and the style of code needed to specify sequential circuits. The VHDL examples given in this book are largely self-explanatory, and students can understand them with ease.

The book is also suitable for a course in logic design that does not include exposure to VHDL. However, some knowledge of VHDL, even at a rudimentary level, is beneficial to the students, and is great preparation for a job as a design engineer.

### **One-Semester Course**

The following material should be covered in lectures:

- Chapter 1—all sections.

- Chapter 2—all sections.

- Chapter 3—sections 3.1 to 3.5.

- Chapter 4—all sections.

- Chapter 5—all sections.

- Chapter 6—all sections.

### **One-Quarter Course**

In a one-quarter course the following material can be covered:

- Chapter 1—all sections.

- Chapter 2—all sections.

- Chapter 3—sections 3.1 to 3.3 and section 3.5.

- Chapter 4—all sections.

- Chapter 5—all sections.

- Chapter 6—sections 6.1 to 6.4.

PREFACE ix

## VHDL

VHDL is a complex language that some instructors feel is too hard for beginning students to grasp. We fully appreciate this issue and have attempted to solve it by presenting only the most important VHDL constructs that are useful for the design and synthesis of logic circuits. Many other language constructs, such as those that have meaning only when using the language for simulation purposes, are omitted. The VHDL material is integrated gradually, with more advanced features presented only at points where their use can be demonstrated in the design of relevant circuits.

The book includes more than 150 examples of VHDL code. These examples illustrate how VHDL is used to describe a wide range of logic circuits, from those that contain only a few gates to those that represent digital systems such as a simple processor.

## **CAD TOOLS**

All of the examples of VHDL code presented in the book are provided on the authors' website at

## www.eecg.toronto.edu/~brown

To gain a more thorough understanding of the VHDL code examples, the reader is encouraged to compile and simulate the code using a commercially-available simulation CAD tool. Toward this end each example of VHDL code on the Authors' website is accompanied by setup files for the widely-used *ModelSim* simulator available from Mentor Graphics. A detailed tutorial is provided that includes step-by-step instructions for obtaining, installing, and using this VHDL simulator.

Modern digital systems are quite large. They contain complex logic circuits that would be difficult to design without using good CAD tools. Our treatment of VHDL should enable the reader to develop VHDL code that specifies logic circuits of varying degrees of complexity. To gain a proper appreciation of the design process, in addition to simulating the behavior of VHDL code (as mentioned above) it is highly beneficial to implement the designs in commercially-available PLDs by using CAD tools.

Some excellent CAD tools are available free of charge, for example, Intel Corporation's Quartus CAD software, which is widely used for implementing designs in programmable logic devices such as FPGAs. The Lite Edition of the Quartus software can be downloaded from Intel's website and used free-of-charge. Intel also provides a set of FPGA-based laboratory boards with accompanying tutorials and laboratory exercises that are appropriate for use with this book in a university setting. This material can be found on the Internet by searching for "Intel FPGA Academic Program".

## SOLVED PROBLEMS

The chapters include examples of solved problems. They provide typical homework problems and show how they may be solved.

## HOMEWORK PROBLEMS

More than 400 homework problems are provided in this book. Answers to selected problems are given at the back. Full solutions to all problems are available to instructors in the accompanying *Solutions Manual*.

## POWERPOINT SLIDES AND SOLUTIONS MANUAL

A set of PowerPoint slides that contain all of the figures in the book is available on the Authors' website. Instructors can request access to these slides, as well as access to the *Solutions Manual* for the book, at:

www.mhhe.com/brownvranesic

## ACKNOWLEDGMENTS

We wish to express our thanks to the people who have helped during the preparation of this book. Dan Vranesic produced a substantial amount of artwork. He and Deshanand Singh also helped with the preparation of the solutions manual, and Tom Czajkowski helped in checking the answers to problems. Matthew Brown edited the text to improve readability, and Andrew Brown helped to create some examples of VHDL code. The reviewers, William Barnes, New Jersey Institute of Technology; Thomas Bradicich, North Carolina State University; James Clark, McGill University; Stephen DeWeerth, Georgia Institute of Technology; Sander Eller, Cal Poly Pomona; Clay Gloster, Jr., North Carolina State University (Raleigh); Carl Hamacher, Queen's University; Vincent Heuring, University of Colorado; Yu Hen Hu, University of Wisconsin; Wei-Ming Lin, University of Texas (San Antonio); Wayne Loucks, University of Waterloo; Kartik Mohanram, Rice University; Jane Morehead, Mississippi State University; Chris Myers, University of Utah; Vojin Oklobdzija, University of California (Davis); James Palmer, Rochester Institute of Technology; Gandhi Puvvada, University of Southern California; Teodoro Robles, Milwaukee School of Engineering; Tatyana Roziner, Boston University; Rob Rutenbar, Carnegie Mellon University; Eric Schwartz, University of Florida; Wen-Tsong Shiue, Oregon State University; Peter Simko, Miami University; Scott Smith, University of Missouri (Rolla); Arun Somani, Iowa State University; Bernard Svihel, University of Texas (Arlington); and Zeljko Zilic, McGill University provided constructive criticism and made numerous suggestions for improvements.

Nicholas Reeder, Sinclair Community College, Dayton, OH, provided excellent proof reading.

Stephen Brown and Zvonko Vranesic

## **CONTENTS**

2.9 Introduction to CAD Tools 59

| INTRODUCTION 1                                                                                                  | • •                                   |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 2.9.2                                                                                                           | 2 3                                   |

| 1.1 Digital Hardware 2 2.9.3                                                                                    |                                       |

| 1.1.1 Standard Chips 4 2.9.4                                                                                    | •                                     |

| 1.1.2 Programmable Logic Devices 4 2.9.5                                                                        | •                                     |

| 1.1.3 Custom-Designed Chips 5 2.9.6                                                                             | 1                                     |

| 1.2 The Design Process 5 2.9.7                                                                                  | 1 &                                   |

| 1.5 Structure of a Compater /                                                                                   | oduction to VHDL 63                   |

| 1.4 Logic Circuit Design in This Book 10 2.10                                                                   | 1 &                                   |

| 1.5 Digital Representation of Information 10                                                                    | Circuits 65                           |

| 1.5.1 Binary Numbers 11 2.10                                                                                    | 1 &                                   |

| 1.5.2 Conversion between Decimal and                                                                            | Circuits 69                           |

| Binary Systems 13 2.10                                                                                          |                                       |

| 1.5.3 ASCII Character Code 14 2.10                                                                              |                                       |

| 1.5.1 Digital and I malog information 11                                                                        | nimization and Karnaugh Maps 73       |

| 1.6 Theory and Practice 16 2.12 Stra                                                                            | tegy for Minimization 81              |

| Problems 17 2.12                                                                                                | .1 Terminology 81                     |

| 2.12                                                                                                            | 2 Minimization Procedure 83           |

| 2.13 Min                                                                                                        | imization of Product-of-Sums Forms 86 |

| Chapter 2 2.14 Inco                                                                                             | ompletely Specified Functions 88      |

| INTRODUCTION TO LOGIC 2.15 Mul                                                                                  | Itiple-Output Circuits 90             |

|                                                                                                                 | icluding Remarks 95                   |

|                                                                                                                 | mples of Solved Problems 95           |

| 2.1 Vaniables and E-mations 20                                                                                  | blems 105                             |

| 2.2 Inversion 22                                                                                                | erences 113                           |

| 2.3 Truth Tables 24                                                                                             | crences 113                           |

| 2.4 Logic Gates and Networks 25 Chapte                                                                          | er 3                                  |

|                                                                                                                 | ER REPRESENTATION AND                 |

| 25 Dealers Alesbur 20                                                                                           |                                       |

| 2.5.1 The Venn Diagram 34                                                                                       | METIC CIRCUITS 115                    |

| <u> </u>                                                                                                        | itional Number Representation 116     |

| 2.5.3 Precedence of Operations 40 3.1.1                                                                         | *                                     |

| 2.6 Synthesis Using AND, OR, and NOT 3.1.2                                                                      | 2 2                                   |

| Gates 40                                                                                                        | Representations 116                   |

|                                                                                                                 | lition of Unsigned Numbers 118        |

| Forms 44 3.2.1                                                                                                  | •                                     |

| 5.2                                                                                                             | Decombosed run-Adder 177              |

| 2.7 NAND and NUK Logic Networks 50 3.2.2                                                                        |                                       |

| <ul><li>2.7 NAND and NOR Logic Networks 50</li><li>2.8 Design Examples 54</li><li>3.2.3</li><li>3.2.3</li></ul> | 2 Ripple-Carry Adder 122              |

2.8.2

2.8.3

Multiplexer Circuit 56

Number Display 58

Chapter 1

3.3.1

3.3.2

Negative Numbers 124

Addition and Subtraction 128

|            | 3.3.3     | Adder and Subtractor Unit 131                |      | 4.6.5    | Concurrent and Sequential Assignment   |

|------------|-----------|----------------------------------------------|------|----------|----------------------------------------|

|            | 3.3.4     | Radix-Complement Schemes* 132                |      |          | Statements 202                         |

|            | 3.3.5     | Arithmetic Overflow 136                      |      | 4.6.6    | Process Statement 203                  |

|            | 3.3.6     | Performance Issues 137                       |      | 4.6.7    | Case Statement 208                     |

| 3.4        |           | ders 138                                     |      | 4.6.8    | VHDL Operators 210                     |

|            | 3.4.1     | Carry-Lookahead Adder 138                    | 4.7  | Conclud  | ling Remarks 215                       |

| 3.5        | _         | of Arithmetic Circuits Using CAD             | 4.8  | Example  | es of Solved Problems 215              |

|            |           | 144                                          |      | Problem  | ns 226                                 |

|            | 3.5.1     | Design of Arithmetic Circuits Using          |      |          |                                        |

|            | 2.5.0     | Schematic Capture 144                        | Cha  | pter     | 5                                      |

|            | 3.5.2     | Design of Arithmetic Circuits Using VHDL 144 | FLI  | P-FLO    | PS, REGISTERS, AND                     |

|            | 3.5.3     | Representation of Numbers in VHDL            | Co   | UNTER    | as 231                                 |

|            | 3.3.3     | Code 147                                     |      |          |                                        |

|            | 3.5.4     | Arithmetic Assignment Statements 149         | 5.1  |          | atch 232                               |

| 3.6        |           | cation 152                                   | 5.2  |          | R Latch 234                            |

|            | 3.6.1     | Array Multiplier for Unsigned                |      | 5.2.1    | Gated SR Latch with NAND Gates 236     |

|            |           | Numbers 154                                  | 5.3  |          | Latch 237                              |

|            | 3.6.2     | Multiplication of Signed Numbers 154         |      | 5.3.1    | Effects of Propagation Delays 239      |

| 3.7        | Other N   | umber Representations 156                    | 5.4  | Edge-Tr  | riggered D Flip-Flops 239              |

|            | 3.7.1     | Fixed-Point Numbers 157                      |      | 5.4.1    | M-S D Flip-Flop 240                    |

|            | 3.7.2     | Floating-Point Numbers 157                   |      | 5.4.2    | Other Types of Edge-Triggered D        |

|            | 3.7.3     | Binary-Coded-Decimal                         |      |          | Flip-Flops 241                         |

|            |           | Representation 159                           |      | 5.4.3    | D Flip-Flops with Clear and Preset 243 |

| 3.8        | -         | es of Solved Problems 163                    |      | 5.4.4    | Flip-Flop Timing Parameters 246        |

|            | Problem   |                                              | 5.5  | -        | Flop 247                               |

|            | Reference | ce 172                                       | 5.6  | -        | Flop 248                               |

| <b>0</b> I |           |                                              | 5.7  |          | ry of Terminology 249                  |

|            | pter      |                                              | 5.8  | Register |                                        |

|            |           | TIONAL-CIRCUIT                               |      | 5.8.1    | Shift Register 250                     |

| BUI        | LDING     | BLOCKS 173                                   |      | 5.8.2    | Parallel-Access Shift Register 251     |

| 4.1        | Multiple  | exers 174                                    | 5.9  | Counter  |                                        |

| 7.1        | 4.1.1     | Synthesis of Logic Functions Using           |      | 5.9.1    | Asynchronous Counters 252              |

|            |           | Multiplexers 177                             |      | 5.9.2    | Synchronous Counters 254               |

|            | 4.1.2     | Multiplexer Synthesis Using Shannon's        |      | 5.9.3    | Counters with Parallel Load 258        |

|            |           | Expansion 180                                |      | -        | ynchronization 260                     |

| 4.2        | Decoder   |                                              | 5.11 |          | ypes of Counters 261                   |

|            | 4.2.1     | Demultiplexers 188                           |      | 5.11.1   | BCD Counter 261                        |

| 4.3        | Encoder   | s 188                                        |      | 5.11.2   | Ring Counter 262                       |

|            | 4.3.1     | Binary Encoders 189                          |      | 5.11.3   | Johnson Counter 265                    |

|            | 4.3.2     | Priority Encoders 190                        |      | 5.11.4   | Remarks on Counter Design 265          |

| 4.4        |           | onverters 191                                | 5.12 | _        | torage Elements with CAD Tools 265     |

| 4.5        |           | tic Comparison Circuits 192                  |      | 5.12.1   | Including Storage Elements in          |

| 4.6        |           | for Combinational Circuits 193               |      | 5 10 0   | Schematics 265                         |

|            | 4.6.1     | Assignment Statements 193                    |      | 5.12.2   | Using VHDL Constructs for Storage      |

|            | 4.6.2     | Selected Signal Assignment 194               | 5 12 | Hoim - V | Elements 268                           |

|            | 4.6.3     | Conditional Signal Assignment 197            | 5.13 |          | HDL Sequential Statements for          |

|            | 4.6.4     | Generate Statements 200                      |      | Kegistei | rs and Counters 273                    |

CONTENTS xiii

|            | 5.13.1 Flip-Flops and Registers with Enable                                                                   | 6.7.2 State Assignment 362                                   |

|------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

|            | Inputs 280                                                                                                    | 6.7.3 Implementation Using D-Type                            |

|            | 5.13.2 Shift Registers with Enable Inputs 283                                                                 | Flip-Flops 363                                               |

| 5.14       | Design Example - Reaction Timer 283<br>5.14.1 Register Transfer Level (RTL) Code 29                           | 6.7.4 Implementation Using JK-Type Flip-Flops 365            |

| 5.15       | Timing Analysis of Flip-flop Circuits 292                                                                     | 6.7.5 Example—A Different Counter 368                        |

|            | 5.15.1 Timing Analysis with Clock Skew 294                                                                    | 6.8 FSM as an Arbiter Circuit 371                            |

| 5.16       | Concluding Remarks 296                                                                                        | 6.9 Analysis of Synchronous Sequential                       |

|            | Examples of Solved Problems 296                                                                               | Circuits 376                                                 |

|            | Problems 303                                                                                                  | 6.10 Algorithmic State Machine (ASM)                         |

|            |                                                                                                               | Charts 380                                                   |

| Cha        | apter 6                                                                                                       |                                                              |

| SY         | NCHRONOUS SEQUENTIAL                                                                                          | 1                                                            |

|            | RCUITS 309                                                                                                    | 6.12 Concluding Remarks 385                                  |

|            | (CC115 30)                                                                                                    | 6.13 Examples of Solved Problems 385                         |

| 6.1        | Basic Design Steps 311                                                                                        | Problems 394                                                 |

|            | 6.1.1 State Diagram 311                                                                                       | Chantar 7                                                    |

|            | 6.1.2 State Table 313                                                                                         | Chapter 7                                                    |

|            | 6.1.3 State Assignment 313                                                                                    | DIGITAL SYSTEM DESIGN 399                                    |

|            | 6.1.4 Choice of Flip-Flops and Derivation of                                                                  | 7.1 Bus Structure 400                                        |

|            | Next-State and Output Expressions 315                                                                         | 7.1.1 Using Tri-State Drivers to Implement a                 |

|            | 6.1.5 Timing Diagram 316                                                                                      | Bus 400                                                      |

| 6.2        | 6.1.6 Summary of Design Steps 318                                                                             | 7.1.2 Using Multiplexers to Implement a                      |

| 0.2        | State-Assignment Problem 322<br>6.2.1 One-Hot Encoding 325                                                    | Bus 402                                                      |

| 6.3        | Mealy State Model 327                                                                                         | 7.1.3 VHDL Code for Specification of Bus                     |

| 6.4        | Design of Finite State Machines Using CAD                                                                     | Structures 404                                               |

| 0.4        | Tools 331                                                                                                     | 7.2 Simple Processor 408                                     |

|            | 6.4.1 VHDL Code for Moore-Type FSMs 332                                                                       | 7.2 A Die Countin a Cinneit 420                              |

|            | 6.4.2 Synthesis of VHDL Code 334                                                                              | 7.4 Shift-and-Add Multiplier 425                             |

|            | 6.4.3 Simulating and Testing the Circuit 335                                                                  | 7.5 Divider 432                                              |

|            | 6.4.4 An Alternative Style of VHDL Code 337                                                                   | 7.6 Arithmetic Mean 442                                      |

|            | 6.4.5 Summary of Design Steps When Using                                                                      | 7.7 Sort Operation 445                                       |

|            | CAD Tools 338                                                                                                 | 7.7 Soft Operation 443  7.8 Clock Synchronization and Timing |

|            | 6.4.6 Specifying the State Assignment in                                                                      | Issues 454                                                   |

|            | VHDL Code 338                                                                                                 | 7.8.1 Clock Distribution 456                                 |

|            | 6.4.7 Specification of Mealy FSMs Using                                                                       | 7.8.2 Flip-Flop Timing Parameters 457                        |

| <i>-</i> - | VHDL 341                                                                                                      | 7.8.3 Asynchronous Inputs to Flip-Flops 458                  |

| 6.5        | Serial Adder Example 343                                                                                      | 7.8.4 Switch Debouncing 459                                  |

|            | <ul><li>6.5.1 Mealy-Type FSM for Serial Adder 343</li><li>6.5.2 Moore-Type FSM for Serial Adder 345</li></ul> | 7.9 Concluding Remarks 461                                   |

|            | 6.5.3 VHDL Code for the Serial Adder 347                                                                      | Problems 461                                                 |

| 6.6        | State Minimization 351                                                                                        | 1 IUUICIIIS 701                                              |

| 0.0        | 6.6.1 Partitioning Minimization Procedure 353                                                                 | Chapter 8                                                    |

|            | 6.6.2 Incompletely Specified FSMs 360                                                                         | OPTIMIZED IMPLEMENTATION OF                                  |

| 6.7        | Design of a Counter Using the Sequential                                                                      | LOGIC FUNCTIONS 465                                          |

| 0.7        | Circuit Approach 361                                                                                          | LUGIC FUNCTIONS 405                                          |

|            | 6.7.1 State Diagram and State Table for a                                                                     | 8.1 Multilevel Synthesis 466                                 |

|            |                                                                                                               |                                                              |

Factoring 467

8.1.1

Modulo-8 Counter 362

|      | 8.1.2 Functional Decomposition 470             | 10.1.2 Gate Optimization 604             |

|------|------------------------------------------------|------------------------------------------|

|      | 8.1.3 Multilevel NAND and NOR Circuits 475     | 10.1.3 Technology Mapping 606            |

| 8.2  | Analysis of Multilevel Circuits 478            | 10.2 Physical Design 609                 |

| 8.3  | Alternative Representations of Logic           | 10.2.1 Placement 609                     |

|      | Functions 483                                  | 10.2.2 Routing 611                       |

|      | 8.3.1 Cubical Representation 483               | 10.2.3 Timing Analysis 613               |

|      | 8.3.2 Binary Decision Diagrams 487             | 10.3 Concluding Remarks 616              |

| 8.4  | Optimization Techniques Based on Cubical       | References 616                           |

|      | Representation 493                             |                                          |

|      | 8.4.1 A Tabular Method for Minimization 493    | Chapter 11                               |

|      | 8.4.2 A Cubical Technique for Minimization 501 | TESTING OF LOGIC CIRCUITS 617            |

|      | 8.4.3 Practical Considerations 508             | 11.1 Fault Model 618                     |

| 8.5  | Concluding Remarks 509                         | 11.1.1 Stuck-at Model 618                |

| 8.6  | Examples of Solved Problems 509                | 11.1.2 Single and Multiple Faults 619    |

| 0.0  | Problems 518                                   | 11.1.3 CMOS Circuits 619                 |

|      | Troblems 516                                   | 11.2 Complexity of a Test Set 619        |

| Cha  | pter 9                                         | 11.3 Path Sensitizing 621                |

|      | YNCHRONOUS SEQUENTIAL                          | 11.3.1 Detection of a Specific Fault 623 |

|      | RCUITS 521                                     | 11.4 Circuits with Tree Structure 625    |

| CIR  | CUIIS 521                                      | 11.5 Random Tests 626                    |

| 9.1  | Asynchronous Behavior 522                      | 11.6 Testing of Sequential Circuits 629  |

| 9.2  | Analysis of Asynchronous Circuits 525          | 11.6.1 Design for Testability 629        |

| 9.3  | Synthesis of Asynchronous Circuits 533         | 11.7 Built-in Self-Test 633              |

| 9.4  | State Reduction 546                            | 11.7.1 Built-in Logic Block Observer 637 |

| 9.5  | State Assignment 560                           | 11.7.2 Signature Analysis 639            |

| ).5  | 9.5.1 Transition Diagram 563                   | 11.7.3 Boundary Scan 640                 |

|      | 9.5.2 Exploiting Unspecified Next-State        | 11.8 Printed Circuit Boards 640          |

|      | Entries 566                                    | 11.8.1 Testing of PCBs 642               |

|      | 9.5.3 State Assignment Using Additional        | 11.8.2 Instrumentation 643               |

|      | State Variables 569                            | 11.9 Concluding Remarks 644              |

|      | 9.5.4 One-Hot State Assignment 575             | Problems 644                             |

| 9.6  | Hazards 576                                    | References 647                           |

|      | 9.6.1 Static Hazards 576                       |                                          |

|      | 9.6.2 Dynamic Hazards 581                      | Appendix A                               |

|      | 9.6.3 Significance of Hazards 583              | VHDL REFERENCE 649                       |

| 9.7  | A Complete Design Example 583                  | A.1 Documentation in VHDL Code 650       |

|      | 9.7.1 The Vending-Machine Controller 583       | A.2 Data Objects 650                     |

| 9.8  | Concluding Remarks 588                         | A.2.1 Data Object Names 650              |

| 9.9  | Examples of Solved Problems 590                | A.2.2 Data Object Values and Numbers 650 |

|      | Problems 598                                   | A.2.3 SIGNAL Data Objects 651            |

|      |                                                | A.2.4 BIT and BIT_VECTOR Types 651       |

| Cha  | pter 10                                        | A.2.5 STD_LOGIC and                      |

| Co   | MPUTER AIDED DESIGN                            | STD_LOGIC_VECTOR Types 652               |

|      | OLS 603                                        | A.2.6 STD_ULOGIC Type 652                |

| 10   | OLD WO                                         | A.2.7 SIGNED and UNSIGNED Types 653      |

| 10.1 | Synthesis 604                                  | A.2.8 INTEGER Type 653                   |

|      | 10.1.1 Netlist Generation 604                  | A.2.9 BOOLEAN Type 654                   |

|      |                                                |                                          |

CONTENTS xv

|       | A.2.10         | ENUMERATION Type 654                  | Арр         | endi     | х В                                   |

|-------|----------------|---------------------------------------|-------------|----------|---------------------------------------|

|       | A.2.11         | CONSTANT Data Objects 654             | IMI         | PLEME    | ENTATION                              |

|       | A.2.12         | VARIABLE Data Objects 655             |             | CHNO     |                                       |

|       | A.2.13         | Type Conversion 655                   | I L         |          | 2001 701                              |

|       | A.2.14         | Arrays 655                            | B.1         | Transis  | stor Switches 702                     |

| A.3   | Operato        | rs 656                                | B.2         | NMOS     | Logic Gates 704                       |

| A.4   |                | Design Entity 657                     | B.3         |          | Logic Gates 707                       |

|       | A.4.1          | ENTITY Declaration 657                | <b>D</b> .5 | B.3.1    | Speed of Logic Gate Circuits 714      |

|       | A.4.2          | Architecture 658                      | B.4         |          | ve Logic System 715                   |

| A.5   | Package        |                                       | B.5         | _        | rd Chips 718                          |

|       |                | ubcircuits 661                        | Б.Э         | B.5.1    |                                       |

| 11.0  | A.6.1          | Declaring a COMPONENT in a            | D (         |          | 7400-Series Standard Chips 718        |

|       | 71.0.1         | Package 663                           | B.6         | _        | mmable Logic Devices 720              |

| A.7   | Concurr        | rent Assignment Statements 664        |             | B.6.1    | Programmable Logic Array (PLA) 721    |

| Λ./   | A.7.1          | Simple Signal Assignment 664          |             | B.6.2    | Programmable Array Logic (PAL) 723    |

|       | A.7.1          | Assigning Signal Values Using         |             | B.6.3    | Programming of PLAs and PALs 725      |

|       | Λ.7.2          | OTHERS 665                            |             | B.6.4    | Complex Programmable Logic Devices    |

|       | A.7.3          | Selected Signal Assignment 666        |             | D 6 5    | (CPLDs) 727                           |

|       | A.7.4          | Conditional Signal Assignment 667     |             | B.6.5    | Field-Programmable Gate Arrays 731    |

|       | A.7.5          | GENERATE Statement 668                | B.7         |          | n Chips, Standard Cells, and Gate     |

| A.8   |                | g an Entity with GENERICs 668         |             | Arrays   | 736                                   |

| A.9   |                | ial Assignment Statements 669         | B.8         | Practic  | al Aspects 738                        |

| Λ.)   | A.9.1          | PROCESS Statement 671                 |             | B.8.1    | MOSFET Fabrication and Behavior 738   |

|       | A.9.2          | IF Statement 671                      |             | B.8.2    | MOSFET On-Resistance 742              |

|       | A.9.2<br>A.9.3 | CASE Statement 672                    |             | B.8.3    | Voltage Levels in Logic Gates 743     |

|       | A.9.4          | Loop Statements 673                   |             | B.8.4    | Noise Margin 745                      |

|       | A.9.5          | Using a Process for a Combinational   |             | B.8.5    | Dynamic Operation of Logic Gates 746  |

|       | 11.7.5         | Circuit 673                           |             | B.8.6    | Power Dissipation in Logic Gates 749  |

|       | A.9.6          | Statement Ordering 674                |             | B.8.7    | Passing 1s and 0s Through Transistor  |

|       | A.9.7          | Using a VARIABLE in a PROCESS 675     |             |          | Switches 751                          |

| Δ 10  |                | ial Circuits 680                      |             | B.8.8    | Transmission Gates 753                |

| 11.10 | A.10.1         | A Gated D Latch 680                   |             | B.8.9    | Fan-in and Fan-out in Logic Gates 755 |

|       | A.10.2         | D Flip-Flop 681                       |             | B.8.10   | Tri-state Drivers 759                 |

|       | A.10.3         | Using a WAIT UNTIL Statement 681      | B.9         | Static I | Random Access Memory                  |

|       | A.10.4         | A Flip-Flop with Asynchronous         |             | (SRAN    | M) 761                                |

|       |                | Reset 682                             |             | B.9.1    | SRAM Blocks in PLDs 762               |

|       | A.10.5         | Synchronous Reset 682                 | B.10        | Implen   | nentation Details for SPLDs, CPLDs,   |

|       | A.10.6         | Registers 684                         |             | and FP   | GAs 763                               |

|       | A.10.7         | Shift Registers 686                   |             | B.10.1   | Implementation in FPGAs 771           |

|       | A.10.8         | Counters 688                          | B.11        | Conclu   | iding Remarks 773                     |

|       | A.10.9         | Using Subcircuits with GENERIC        |             |          | eles of Solved Problems 773           |

|       |                | Parameters 688                        | ~,12        | Problei  |                                       |

|       | A.10.10        | A Moore-Type Finite State Machine 692 |             |          | nces 790                              |

|       |                | A Mealy-Type Finite State Machine 696 |             | Keielei  | 170                                   |

| A.11  |                | n Errors in VHDL Code 696             | AN          | SWER     | s 791                                 |

|       |                | ling Remarks 699                      | . A. 1      | ~ ,, 111 | ~ · · · ·                             |

| _     |                | ces 700                               | IND         | EX 8     | 805                                   |

## **Instructors:** Student Success Starts with You

## Tools to enhance your unique voice

Want to build your own course? No problem. Prefer to use an OLC-aligned, prebuilt course? Easy. Want to make changes throughout the semester? Sure. And you'll save time with Connect's auto-grading too.

Laptop: McGraw Hill; Woman/dog: George Doyle/Getty Images

## Study made personal

Incorporate adaptive study resources like SmartBook® 2.0 into your course and help your students be better prepared in less time. Learn more about the powerful personalized learning experience available in SmartBook 2.0 at www.mheducation.com/highered/connect/smartbook

## Affordable solutions, added value

Make technology work for you with LMS integration for single sign-on access, mobile access to the digital textbook, and reports to quickly show you how each of your students is doing. And with our Inclusive Access program you can provide all these tools at a discount to your students. Ask your McGraw Hill representative for more information.

Padlock: Jobalou/Getty Images

## Solutions for your challenges

A product isn't a solution. Real solutions are affordable, reliable, and come with training and ongoing support when you need it and how you want it. Visit www. supportateverystep.com for videos and resources both you and your students can use throughout the semester.

Checkmark: Jobalou/Getty Images

## Students: Get Learning that Fits You

## Effective tools for efficient studying

Connect is designed to help you be more productive with simple, flexible, intuitive tools that maximize your study time and meet your individual learning needs. Get learning that works for you with Connect.

## Study anytime, anywhere

Download the free ReadAnywhere app and access your online eBook, SmartBook 2.0, or Adaptive Learning Assignments when it's convenient, even if you're offline. And since the app automatically syncs with your Connect account, all of your work is available every time you open it. Find out more at www.mheducation.com/readanywhere

"I really liked this app—it made it easy to study when you don't have your textbook in front of you."

- Jordan Cunningham, Eastern Washington University

## Everything you need in one place

Your Connect course has everything you need—whether reading on your digital eBook or completing assignments for class, Connect makes it easy to get your work done.

Calendar: owattaphotos/Getty Images

## Learning for everyone

McGraw Hill works directly with Accessibility Services Departments and faculty to meet the learning needs of all students. Please contact your Accessibility Services Office and ask them to email accessibility@mheducation.com, or visit www.mheducation.com/about/accessibility for more information.

chapter

1

## **INTRODUCTION**

## **CHAPTER OBJECTIVES**

In this chapter you will be introduced to:

- Digital hardware components

- An overview of the design process

- Binary numbers

- Digital representation of information

This book is about logic circuits—the circuits from which computers are built. Proper understanding of logic circuits is vital for today's electrical and computer engineers. These circuits are the key ingredient of computers and are also used in many other applications. They are found in commonly used products like music and video players, electronic games, digital watches, cameras, televisions, printers, and many household appliances, as well as in large systems, such as telephone networks, Internet equipment, television broadcast equipment, industrial control units, and medical instruments. In short, logic circuits are an important part of almost all modern products.

The material in this book will introduce the reader to the many issues involved in the design of logic circuits. It explains the key ideas with simple examples and shows how complex circuits can be derived from elementary ones. We cover the classical theory used in the design of logic circuits because it provides the reader with an intuitive understanding of the nature of such circuits. But, throughout the book, we also illustrate the modern way of designing logic circuits using sophisticated *computer aided design (CAD)* software tools. The CAD methodology adopted in the book is based on the industry-standard design language called *VHDL*. Design with VHDL is first introduced in Chapter 2, and usage of VHDL and CAD tools is an integral part of each chapter in the book.

Logic circuits are implemented electronically, using transistors on an integrated circuit chip. Commonly available chips that use modern technology may contain more than a billion transistors, as in the case of some computer processors. The basic building blocks for such circuits are easy to understand, but there is nothing simple about a circuit that contains billions of transistors. The complexity that comes with large circuits can be handled successfully only by using highly organized design techniques. We introduce these techniques in this chapter, but first we briefly describe the hardware technology used to build logic circuits.

## 1.1 DIGITAL HARDWARE

Logic circuits are used to build computer hardware, as well as many other types of products. All such products are broadly classified as *digital hardware*. The reason that the name *digital* is used will be explained in Section 1.5—it derives from the way in which information is represented in computers, as electronic signals that correspond to digits of information.

The technology used to build digital hardware has evolved dramatically over the past few decades. Until the 1960s logic circuits were constructed with bulky components, such as transistors and resistors that came as individual parts. The advent of integrated circuits made it possible to place a number of transistors, and thus an entire circuit, on a single chip. In the beginning these circuits had only a few transistors, but as the technology improved they became more complex. Integrated circuit chips are manufactured on a silicon wafer, such as the one shown in Figure 1.1. The wafer is cut to produce the individual chips, which are then placed inside a special type of chip package. By 1970 it was possible to implement all circuitry needed to realize a microprocessor on a single chip. Although early microprocessors had modest computing capability by today's standards, they opened the door for the information processing revolution by providing the means for implementation of affordable personal computers.

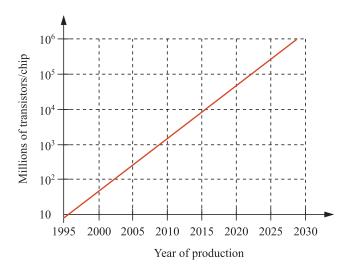

About 30 years ago Gordon Moore, chairman of Intel Corporation, observed that integrated circuit technology was progressing at an astounding rate, approximately doubling the number of transistors that could be placed on a chip every two years. This phenomenon is informally known as *Moore's law*. Thus in the early 1990s microprocessors could be

Figure 1.1 A silicon wafer.

manufactured with a few million transistors, and by the late 1990s it became possible to fabricate chips that had tens of millions of transistors. Presently, chips can be manufactured containing billions of transistors.

Moore's law is expected to continue to hold true for a number of years. A consortium of integrated circuit associations produces a forecast of how the technology is expected to evolve. Known as the *International Roadmap for Devices and Systems (IRDS)*, this forecast discusses many aspects of technology, including the maximum number of transistors that can be manufactured in a given chip area. An example of data that can be derived from the roadmap is given in Figure 1.2. It indicates how the maximum number of transistors that can be manufactured on a single chip has changed over time—chips with about 10 million transistors could be successfully manufactured in 1995, and this number has steadily increased, leading to modern chips that have over a billion transistors. The roadmap predicts that chips with more than 100 billion transistors will be possible by the year 2025. There is no doubt that this technology will have a huge impact on all aspects of people's lives.

The designer of digital hardware may be faced with designing logic circuits that can be implemented on a single chip or designing circuits that involve a number of chips placed on a *printed circuit board (PCB)*. Frequently, some of the logic circuits can be realized in existing chips that are readily available. This situation simplifies the design task and shortens the time needed to develop the final product. Before we discuss the design process in detail, we should introduce the different types of integrated circuit chips that may be used.

There exists a large variety of chips that implement various functions that are useful in the design of digital hardware. The chips range from simple ones with low functionality to extremely complex chips. For example, a digital hardware product may require a microprocessor to perform some arithmetic operations, memory chips to provide storage capability,

**Figure 1.2** An estimate of the maximum number of transistors per chip over time.

and interface chips that allow easy connection to input and output devices. Such chips are available from various vendors.

For many digital hardware products, it is also necessary to design and build some logic circuits from scratch. For implementing these circuits, three main types of chips may be used: standard chips, programmable logic devices, and custom chips. These are discussed next.

## 1.1.1 STANDARD CHIPS

Numerous chips are available that realize some commonly used logic circuits. We will refer to these as *standard chips*, because they usually conform to an agreed-upon standard in terms of functionality and physical configuration. Each standard chip contains a small amount of circuitry (usually involving fewer than 100 transistors) and performs a simple function. To build a logic circuit, the designer chooses the chips that perform whatever functions are needed and then defines how these chips should be interconnected to realize a larger logic circuit.

Standard chips were popular for building logic circuits until the early 1980s. However, as integrated circuit technology improved, it became inefficient to use valuable space on PCBs for chips with low functionality. Another drawback of standard chips is that the functionality of each chip is fixed and cannot be changed.

## 1.1.2 PROGRAMMABLE LOGIC DEVICES

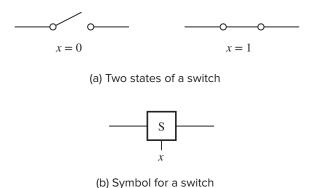

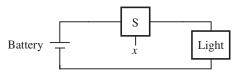

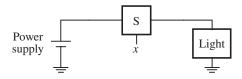

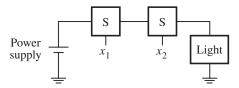

In contrast to standard chips that have fixed functionality, it is possible to construct chips that contain circuitry which can be configured by the user to implement a wide range of different logic circuits. These chips have a very general structure and include a collection of *programmable switches* that allow the internal circuitry in the chip to be configured in many different ways. The designer can implement whatever functions are required for a particular application by setting the programmable switches as needed. The switches are

programmed by the end user, rather than when the chip is manufactured. Such chips are known as *programmable logic devices (PLDs)*.

PLDs are available in a wide range of sizes, and can be used to implement very large logic circuits. The most commonly used type of PLD is known as a *field-programmable gate array (FPGA)*. The largest FPGAs contain billions of transistors and support the implementation of complex digital systems. An FPGA consists of a large number of small logic circuit elements, which can be connected together by using programmable switches in the FPGA. Because of their high capacity, and their capability to be tailored to meet the requirements of a specific application, FPGAs are widely used today.

## 1.1.3 CUSTOM-DESIGNED CHIPS

FPGAs are available as off-the-shelf components that can be purchased from different suppliers. Because they are programmable, they can be used to implement most logic circuits found in digital hardware. However, they also have a drawback in that the programmable switches consume valuable chip area and limit the speed of operation of implemented circuits. Thus in some cases FPGAs may not meet the desired performance or cost objectives. In such situations it is possible to design a chip from scratch; namely, the logic circuitry that must be included on the chip is designed first and then the chip is manufactured by a company that has the fabrication facilities. This approach is known as *custom* or *semi-custom design*, and such chips are often called *application-specific integrated circuits (ASICs)*.

The main advantage of a custom chip is that its design can be optimized for a specific task; hence it usually leads to better performance. It is possible to include a larger amount of logic circuitry in a custom chip than would be possible in other types of chips. The cost of producing such chips is high, but if they are used in a product that is sold in large quantities, then the cost per chip, amortized over the total number of chips fabricated, may be lower than the total cost of off-the-shelf chips that would be needed to implement the same function(s). Moreover, if a single chip can be used instead of multiple chips to achieve the same goal, then a smaller area is needed on a PCB that houses the chips in the final product. This results in a further reduction in cost.

A disadvantage of the custom-design approach is that manufacturing a custom chip often takes a considerable amount of time, on the order of months. In contrast, if an FPGA can be used instead, then the chips are programmed by the end user and no manufacturing delays are involved.

## **1.2** THE DESIGN PROCESS

The availability of computer-based tools has greatly influenced the design process in a wide variety of environments. For example, designing an automobile is similar in the general approach to designing a furnace or a computer. Certain steps in the development cycle must be performed if the final product is to meet the specified objectives.

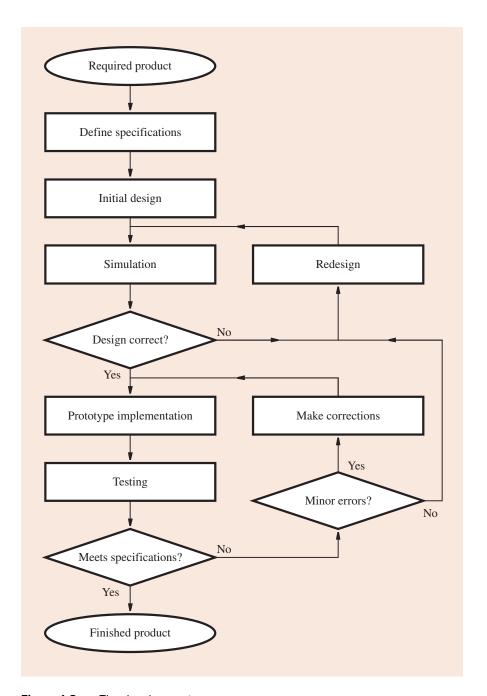

The flowchart in Figure 1.3 depicts a typical development process. We assume that the process is to develop a product that meets certain expectations. The most obvious requirements are that the product must function properly, that it must meet an expected level of performance, and that its cost should not exceed a given target.

**Figure 1.3** The development process.

The process begins with the definition of product specifications. The essential features of the product are identified, and an acceptable method of evaluating the implemented features in the final product is established. The specifications must be tight enough to ensure that the developed product will meet the general expectations, but should not be unnecessarily constraining (that is, the specifications should not prevent design choices that may lead to unforeseen advantages).

From a complete set of specifications, it is necessary to define the general structure of an initial design of the product. This step is difficult to automate. It is usually performed by a human designer because there is no clear-cut strategy for developing a product's overall structure—it requires considerable design experience and intuition.

After the general structure is established, CAD tools are used to work out the details. Many types of CAD tools are available, ranging from those that help with the design of individual parts of the system to those that allow the entire system's structure to be represented in a computer. When the initial design is finished, the results must be verified against the original specifications. Traditionally, before the advent of CAD tools, this step involved constructing a physical model of the designed product, usually including just the key parts. Today it is seldom necessary to build a physical model. CAD tools enable designers to simulate the behavior of incredibly complex products, and such simulations are used to determine whether the obtained design meets the required specifications. If errors are found, then appropriate changes are made and the verification of the new design is repeated through simulation. Although some design flaws may escape detection via simulation, usually all but the most subtle problems are discovered in this way.

When the simulation indicates that the design is correct, a complete physical prototype of the product is constructed. The prototype is thoroughly tested for conformance with the specifications. Any errors revealed in the testing must be fixed. The errors may be minor, and often they can be eliminated by making small corrections directly on the prototype of the product. In case of large errors, it is necessary to redesign the product and repeat the steps explained above. When the prototype passes all the tests, then the product is deemed to be successfully designed and it can go into production.

## **1.3** STRUCTURE OF A COMPUTER

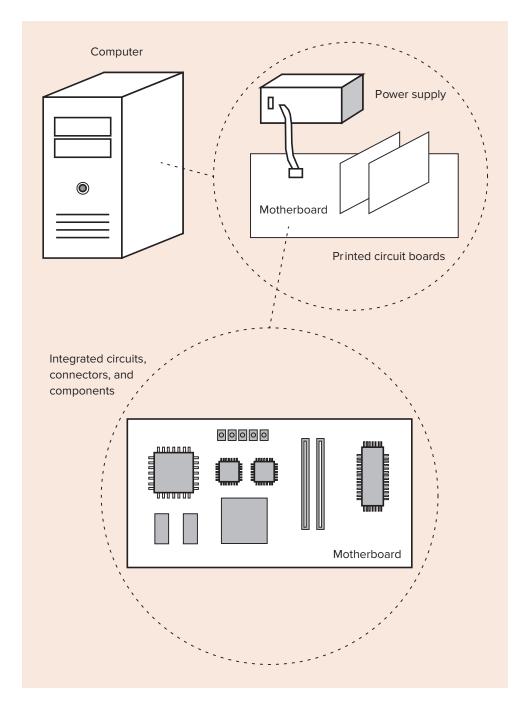

To understand the role that logic circuits play in digital systems, consider the structure of a typical computer, as illustrated in Figure 1.4a. The computer case houses a number of printed circuit boards (PCBs), a power supply, and (not shown in the figure) storage units, like a hard disk and DVD or CD-ROM drives. Each unit is plugged into a main PCB, called the *motherboard*. As indicated on the bottom of the figure, the motherboard holds several integrated circuit chips, and it provides slots for connecting other PCBs, such as audio, video, and network boards.

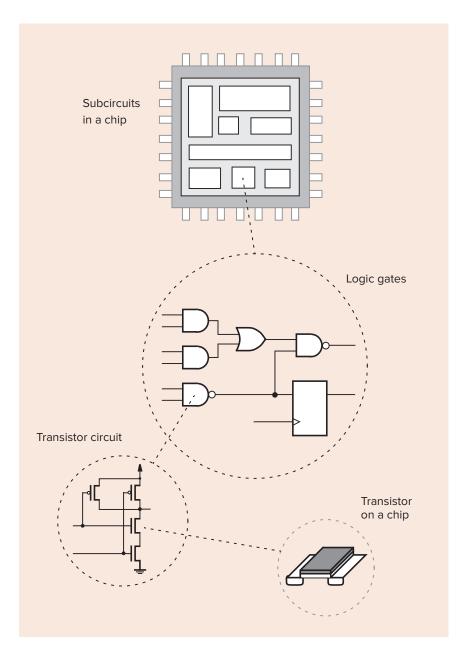

Figure 1.4b illustrates the structure of an integrated circuit chip. The chip comprises a number of subcircuits, which are interconnected to build the complete circuit. Examples of subcircuits are those that perform arithmetic operations, store data, or control the flow of data. Each of these subcircuits is a logic circuit. As shown in the middle of the figure, a logic circuit comprises a network of connected *logic gates*. Each logic gate performs a very simple function, and more complex operations are realized by connecting gates together. Logic gates are built with transistors, which in turn are implemented by fabricating various layers of material on a silicon chip.

**Figure 1.4** A digital hardware system (Part *a*).

**Figure 1.4** A digital hardware system (Part *b*).

This book is primarily concerned with the center portion of Figure 1.4b—the design of logic circuits. We explain how to design circuits that perform important functions, such as adding, subtracting, or multiplying numbers, counting, storing data, and controlling the processing of information. We show how the behavior of such circuits is specified, how the circuits are designed for minimum cost or maximum speed of operation, and how the circuits can be tested to ensure correct operation. We also briefly explain how transistors operate, and how they are built on silicon chips.

## 1.4 LOGIC CIRCUIT DESIGN IN THIS BOOK

In this book we use a modern design approach based on the VHDL hardware description language and CAD tools to illustrate many aspects of logic circuit design. We selected this technology because it is widely used in industry and because it enables the readers to implement their designs in FPGA chips, as discussed below. This technology is particularly well-suited for educational purposes because many readers have access to facilities for using CAD tools and programming FPGA devices.

To gain practical experience and a deeper understanding of logic circuits, we advise the reader to implement the examples in this book using CAD software. Most of the major vendors of CAD systems provide their software at no cost to university students for educational use. Some examples are Intel, Cadence, Mentor Graphics, Synopsys, and Xilinx. The CAD systems offered by any of these companies can be used equally well with this book. Two examples of CAD systems that are particularly well-suited for use with this book are those provided by Intel and Xilinx. The CAD tools from both of these corporations support all phases of the design cycle for logic circuits and are powerful and easy to use. The reader is encouraged to visit the website for these companies, where the software tools and tutorials that explain their use can be downloaded and installed onto any personal computer.

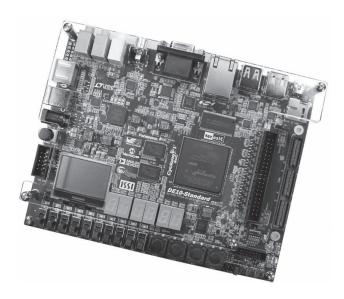

To facilitate experimentation with logic circuits, some FPGA manufacturers provide special PCBs that include one or more FPGA chips and an interface to a personal computer. Once a logic circuit has been designed using the CAD tools, the circuit can be *programmed* into an FPGA on the board. Inputs can then be applied to the FPGA by way of switches and other devices, and the generated outputs can be examined. An example of such a board is depicted in Figure 1.5. This type of board is an excellent vehicle for learning about logic circuits, because it provides a collection of simple input and output devices. Many illustrative experiments can be carried out by designing and implementing logic circuits using the FPGA chip on the board.

## 1.5 DIGITAL REPRESENTATION OF INFORMATION

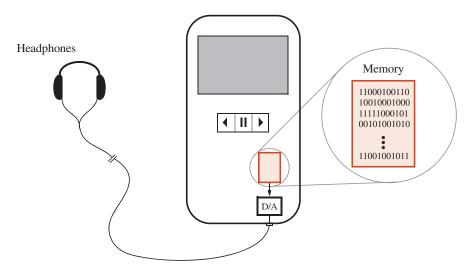

In Section 1.1 we mentioned that information is represented in logic circuits as electronic signals. Each of these signals can be thought of as representing one *digit* of information. To make the design of logic circuits easier, each digit is allowed to take on only two possible values, usually denoted as 0 and 1. These logic values are implemented as voltage levels in a circuit; the value 0 is usually represented as 0 V (ground), and the value 1 is the voltage

Figure 1.5 An FPGA board.

level of the circuit's power supply. As we discuss in Appendix B, typical power-supply voltages in logic circuits range from 1 V DC to 5 V DC.

In general, all information in logic circuits is represented as combinations of 0 and 1 digits. Before beginning our discussion of logic circuits in Chapter 2, it will be helpful to examine how numbers, alphanumeric data (text), and other information can be represented using the digits 0 and 1.

## 1.5.1 BINARY NUMBERS

In the familiar decimal system, a number consists of digits that have 10 possible values, from 0 to 9, and each digit represents a multiple of a power of 10. For example, the number 8547 represents  $8 \times 10^3 + 5 \times 10^2 + 4 \times 10^1 + 7 \times 10^0$ . We do not normally write the powers of 10 with the number, because they are implied by the positions of the digits. In general, a decimal integer is expressed by an *n*-tuple comprising *n* decimal digits

$$D=d_{n-1}d_{n-2}\cdots d_1d_0$$

which represents the value

$$V(D) = d_{n-1} \times 10^{n-1} + d_{n-2} \times 10^{n-2} + \dots + d_1 \times 10^1 + d_0 \times 10^0$$

This is referred to as the *positional number representation*.

Because the digits have 10 possible values and each digit is weighted as a power of 10, we say that decimal numbers are *base*-10 numbers. Decimal numbers are familiar, convenient, and easy to understand. However, since digital circuits represent information using only the values 0 and 1, it is not practical to have digits that can assume ten values. In these circuits it is more appropriate to use the binary, or *base*-2, system which has only the digits

0 and 1. Each binary digit is called a *bit*. In the binary number system, the same positional number representation is used so that

$$B = b_{n-1}b_{n-2} \cdots b_1b_0$$

represents an integer that has the value

$$\begin{split} V(B) &= b_{n-1} \times 2^{n-1} + b_{n-2} \times 2^{n-2} + \dots + b_1 \times 2^1 + b_0 \times 2^0 \\ &= \sum_{i=0}^{n-1} b_i \times 2^i \end{split} \tag{1.1}$$

For example, the binary number 1101 represents the value

$$V = 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0$$

Because a particular digit pattern has different meanings for different bases, we will indicate the base as a subscript when there is potential for confusion. Thus to specify that 1101 is a base-2 number, we will write  $(1101)_2$ . Evaluating the preceding expression for V gives V = 8 + 4 + 1 = 13. Hence

$$(1101)_2 = (13)_{10}$$

The range of integers that can be represented by a binary number depends on the number of bits used. Table 1.1 lists the first 15 positive integers and shows their binary representations using four bits. An example of a larger number is  $(10110111)_2 = (183)_{10}$ . In general, using n bits allows representation of positive integers in the range 0 to  $2^n - 1$ .

In a binary number the rightmost bit is usually referred to as the *least-significant bit (LSB)*. The left-most bit, which has the highest power of 2 associated with it, is called the

Table 1.1 Numbers in decimal and binary.

| Decimal representation | Binary representation |

|------------------------|-----------------------|

| 00                     | 0000                  |

| 01                     | 0001                  |

| 02                     | 0010                  |

| 03                     | 0011                  |

| 04                     | 0100                  |

| 05                     | 0101                  |

| 06                     | 0110                  |

| 07                     | 0111                  |

| 08                     | 1000                  |

| 09                     | 1001                  |

| 10                     | 1010                  |

| 11                     | 1011                  |

| 12                     | 1100                  |

| 13                     | 1101                  |

| 14                     | 1110                  |

| 15                     | 1111                  |

most-significant bit (MSB). In digital systems it is often convenient to consider several bits together as a group. A group of four bits is called a *nibble*, and a group of eight bits is called a *byte*.

## 1.5.2 CONVERSION BETWEEN DECIMAL AND BINARY SYSTEMS